Computer organization and architecture miscellaneous

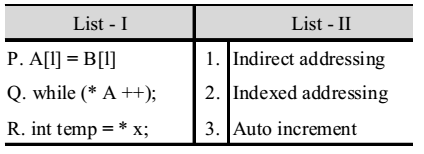

- Match each of the high level language statements given on the left hand side with the most natural addressing mode from those listed on the right hand side.

-

View Hint View Answer Discuss in Forum

(c) is the answer

A [i] = B [i]; Indexed addressing

While [*A + +]; Auto increment

temp = *x; Indirect addressing.Correct Option: C

(c) is the answer

A [i] = B [i]; Indexed addressing

While [*A + +]; Auto increment

temp = *x; Indirect addressing.

- Consider a three word machine instruction:

ADD A[R0], @ B

The first operand (destination) “A[R0]” uses indexed addressing mode with R0 as the index register. The second operand (source) “@B” uses indirect addressing mode. A and B are memory addresses residing at the second and the third words, respectively. The first word of the instruction specifies the opcode, the index register designation and the source and destination addressing modes. During execution of ADD instruction, the two operands are added and stored in the destination (first operand). The number of memory cycles needed during the execution cycle of the instruction is

-

View Hint View Answer Discuss in Forum

The given instruction can be written as:

A [R0] ← A[R0] + @B

So, 2 memory accesses for fetching operand B, 1 for A[R0] and 1 for write back into A[R0]...

Hence 4 memory accesses are required in total.

⇒ Hence option (B) is the correct answer.

Delay slots in pipeline caused due to a branch instruction 2.Correct Option: B

The given instruction can be written as:

A [R0] ← A[R0] + @B

So, 2 memory accesses for fetching operand B, 1 for A[R0] and 1 for write back into A[R0]...

Hence 4 memory accesses are required in total.

⇒ Hence option (B) is the correct answer.

Delay slots in pipeline caused due to a branch instruction 2.

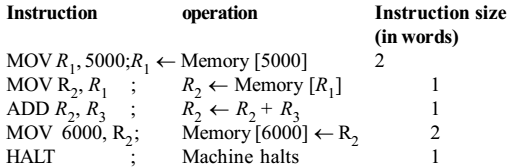

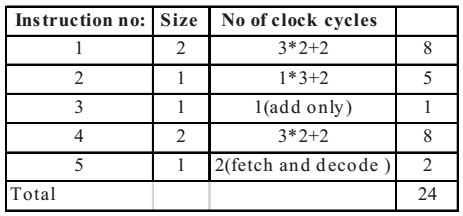

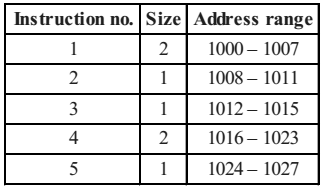

Direction: Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

- Let the clock cycles required for vavious operations be as follows: Register to/from memory transfer: 3 clock cycles

Add with both operands in register: 1 clock cycle

Instruction fetch and decode: 2 clock cycles per word

The total number of clock cycles requires to execute the program is

-

View Hint View Answer Discuss in Forum

The clock cycles are per block so if an instruction size is 2 then it requires twice no. of clock cycles.

Correct Option: B

The clock cycles are per block so if an instruction size is 2 then it requires twice no. of clock cycles.

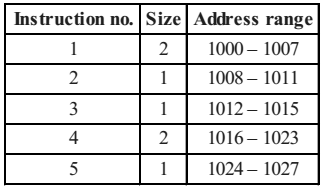

- Consider that the memory is byte addressable with size 32 bit, and the program has been loaded starting from memory location 1000 (decimal). If an Interrupt occurrs while the CPU has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

-

View Hint View Answer Discuss in Forum

Byte addressable so 1 word require 4 bytes.

Next location 1028. CPU has executed the HALT instruction so next time the CPU will resume at next location i.e. 1028 which would be at the top of stack. Hence (d) is correct option.Correct Option: D

Byte addressable so 1 word require 4 bytes.

Next location 1028. CPU has executed the HALT instruction so next time the CPU will resume at next location i.e. 1028 which would be at the top of stack. Hence (d) is correct option.

- Consider a new instruction named branch-on-bit-set (mnemonic bbs). The instruction “bbs reg, pos, label” jumps to label if bit in position pos of register operand reg is one. A register is 32 bit wide and the bits are numbered 0 to 32, bit in position 0 being the least significant. Consider the following emulation of this instruction on a processor that does not have bbs implemented. tem ← reg and mask Branch to lable if temp is non-zero The variable temp is a temporary register. For correct emulation, the variable mask must be generated by

-

View Hint View Answer Discuss in Forum

From the given conditions it can be determined that we have to set all the other bits to 0 in temp, as the position pos is the only deciding factor in jumping to the label. If the left shift over 1 is done by the pos number then the mask register can have 1 in pos place, which is required. Thus, is the option mask ← 0 × 1 << pos is correct.

Correct Option: A

From the given conditions it can be determined that we have to set all the other bits to 0 in temp, as the position pos is the only deciding factor in jumping to the label. If the left shift over 1 is done by the pos number then the mask register can have 1 in pos place, which is required. Thus, is the option mask ← 0 × 1 << pos is correct.