Computer organization and architecture miscellaneous

- A device employing INTR line for device interrupt puts the CALL instruction on the data bus while

-

View Hint View Answer Discuss in Forum

INTR is a signal which if enabled then microprocessor has interrupt enabled. It receives high INR signal & activates INTA signal, so another request can’t be accepted till CPU is busy in servicing interrupt. Hence (a) is correct option.

Correct Option: A

INTR is a signal which if enabled then microprocessor has interrupt enabled. It receives high INR signal & activates INTA signal, so another request can’t be accepted till CPU is busy in servicing interrupt. Hence (a) is correct option.

- What are the sates of the Auxiliary Carry (AC) and carry Flag (CY) after executing the following 8085 program?

MVI H, 5DH

MVI L, 6BH

MOV A, H

ADD L

-

View Hint View Answer Discuss in Forum

The MVI instruction loads 5DH in H register and 6BH in L register respectively. The MOV instruction moves the contents of the source to the destination i.e., the contents of register H are copied in accumulator A. And the ADD instruction adds the contents of destination register i.e., L to the accumulator A. Thus, the program performs the above functions and adds 5DH and 6BH to obtain the result as 0101 1101 (5DH) + 0110 1011 (6BH) = 1100 1000 The result 1100 1000 is stored in the flags as

Thus, the value stored in AC and CY is 1 and 0 respectively as the value of P flag is passed to AC as a carry.Correct Option: C

The MVI instruction loads 5DH in H register and 6BH in L register respectively. The MOV instruction moves the contents of the source to the destination i.e., the contents of register H are copied in accumulator A. And the ADD instruction adds the contents of destination register i.e., L to the accumulator A. Thus, the program performs the above functions and adds 5DH and 6BH to obtain the result as 0101 1101 (5DH) + 0110 1011 (6BH) = 1100 1000 The result 1100 1000 is stored in the flags as

Thus, the value stored in AC and CY is 1 and 0 respectively as the value of P flag is passed to AC as a carry.

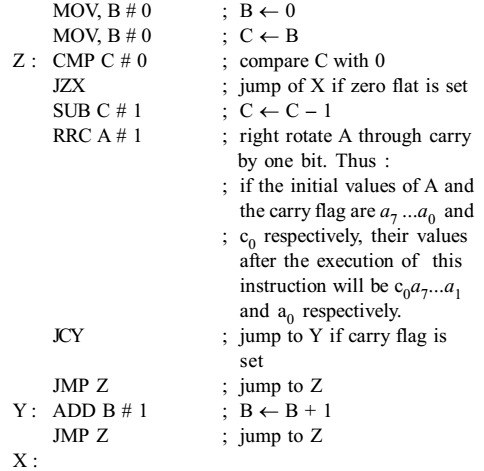

Direction: Consider the following assembly language program for a hypothetical processor. A, B and C are 8 registers. The meanings of various instructions are shown as comments.

- Which of the following instructions when inserted at location X will ensure that the value of register A after program execution is the same as its initial value?

-

View Hint View Answer Discuss in Forum

In the end of program execution to check whether both initial and final value of register A is A0, we need to right rotate register A through carry by one bit. Hence (a) is correct option.

Correct Option: A

In the end of program execution to check whether both initial and final value of register A is A0, we need to right rotate register A through carry by one bit. Hence (a) is correct option.

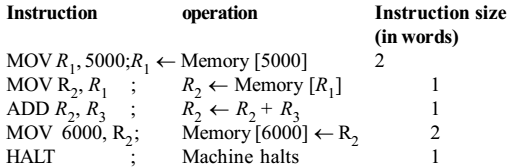

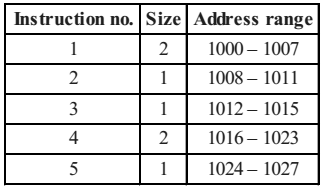

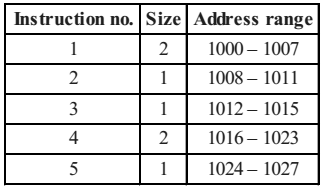

Direction: Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

- Consider that the memory is byte addressable with size 32 bit, and the program has been loaded starting from memory location 1000 (decimal). If an Interrupt occurrs while the CPU has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

-

View Hint View Answer Discuss in Forum

Byte addressable so 1 word require 4 bytes.

Next location 1028. CPU has executed the HALT instruction so next time the CPU will resume at next location i.e. 1028 which would be at the top of stack. Hence (d) is correct option.Correct Option: D

Byte addressable so 1 word require 4 bytes.

Next location 1028. CPU has executed the HALT instruction so next time the CPU will resume at next location i.e. 1028 which would be at the top of stack. Hence (d) is correct option.

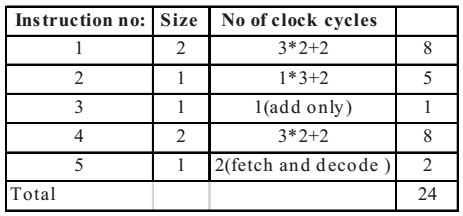

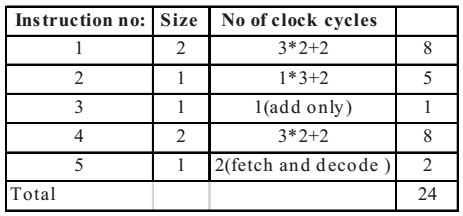

- Let the clock cycles required for vavious operations be as follows: Register to/from memory transfer: 3 clock cycles

Add with both operands in register: 1 clock cycle

Instruction fetch and decode: 2 clock cycles per word

The total number of clock cycles requires to execute the program is

-

View Hint View Answer Discuss in Forum

The clock cycles are per block so if an instruction size is 2 then it requires twice no. of clock cycles.

Correct Option: B

The clock cycles are per block so if an instruction size is 2 then it requires twice no. of clock cycles.