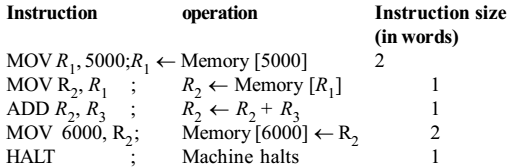

Direction: Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

-

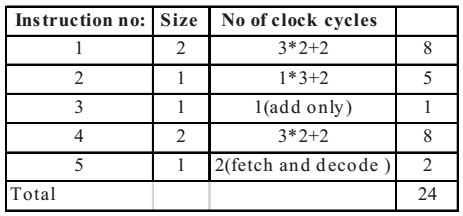

Let the clock cycles required for vavious operations be as follows: Register to/from memory transfer: 3 clock cycles

Add with both operands in register: 1 clock cycle

Instruction fetch and decode: 2 clock cycles per word

The total number of clock cycles requires to execute the program is

-

- 29

- 24

- 23

- 20

- 29

Correct Option: B

The clock cycles are per block so if an instruction size is 2 then it requires twice no. of clock cycles.