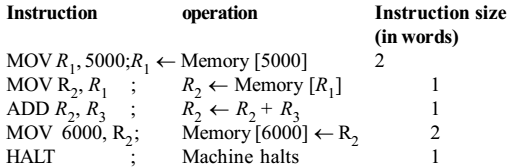

Direction: Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

-

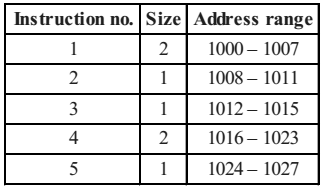

Consider that the memory is byte addressable with size 32 bit, and the program has been loaded starting from memory location 1000 (decimal). If an Interrupt occurrs while the CPU has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

-

- 1007

- 1020

- 1024

- 1028

- 1007

Correct Option: D

Byte addressable so 1 word require 4 bytes.

Next location 1028. CPU has executed the HALT instruction so next time the CPU will resume at next location i.e. 1028 which would be at the top of stack. Hence (d) is correct option.