Computer organization and architecture miscellaneous

- A machine has a 32-bit architecture, with 1-word long instructions. It has 64 registers, each of which is 32 bits long. It needs to support 45 instructions, which have an immediate operand in addition to two register operands. Assuming that the immediate operand is an unsigned integer, the maximum value of the immediate operand is ______ .

-

View Hint View Answer Discuss in Forum

(i) Given is 32-bit architecture machine with 1 word long instruction; so, the instruction size is 32 bit.

(ii) As the machine need to support 45 instructions, the number of bits required in the “opcode field” is 6 bits, because,

5-bits: 25 = 32 (Not sufficient)

6-bits: 26 = 64 (Sufficient)

(iii) As the machine has 64 registers, so to uniquely identify a register out of those 64 registers, we need 6-bits. (using the similar argument as above) As each instruction has 2 register operands, so 6 + 6 = 12 bits are needed for them. So, finally instruction will took like as follows:

(Total = 32 bits)

(iv) As 14-bits are available for immediate operand, the max value will be 214 = 16384. However one value will be used for “Zero” also as the operand is an “unsigned integer”. So, finally, the maximum value that the immediate operand can take = 214 – 1 = 16383.Correct Option: C

(i) Given is 32-bit architecture machine with 1 word long instruction; so, the instruction size is 32 bit.

(ii) As the machine need to support 45 instructions, the number of bits required in the “opcode field” is 6 bits, because,

5-bits: 25 = 32 (Not sufficient)

6-bits: 26 = 64 (Sufficient)

(iii) As the machine has 64 registers, so to uniquely identify a register out of those 64 registers, we need 6-bits. (using the similar argument as above) As each instruction has 2 register operands, so 6 + 6 = 12 bits are needed for them. So, finally instruction will took like as follows:

(Total = 32 bits)

(iv) As 14-bits are available for immediate operand, the max value will be 214 = 16384. However one value will be used for “Zero” also as the operand is an “unsigned integer”. So, finally, the maximum value that the immediate operand can take = 214 – 1 = 16383.

- Consider the following code sequence having five instructions I1 to I5. Each of these instructions has the following format.

OP Ri, Rj, Rk

Where operation Op is performed on contents of registers Rj and Rk and the result is stored in register Ri.

I1: ADD R1, R2, R3

I2: MUL R7, R1, R3

I3: SUB R4, R1, R5

I4: ADD R3, R2, R4

I5: MUL R7, R8, R9

Consider the following three statements.

S1: There is an anti-dependence between instruction I2 and I5

S2: There is an anti-dependence between instructions I2 and I4

S3: Within an instruction pipeline an anti-dependence always creates one or more stalls Which one of above statements is/are correct?

-

View Hint View Answer Discuss in Forum

(I1) R1 ← R2 + R3

(I2) R7 ← R1 × R3

(I3) R4 ← R1 – R5

(I4) R3 ← R2 + R4

(I5) R7 ← R8 × R9

Anti dependence

(i) -------------- = x

(j) X : --------------

then i and j are anti – dependence

Hence I2 and I4 are anti-dependence

⇒ Anti-dependence create stall in pipelineCorrect Option: D

(I1) R1 ← R2 + R3

(I2) R7 ← R1 × R3

(I3) R4 ← R1 – R5

(I4) R3 ← R2 + R4

(I5) R7 ← R8 × R9

Anti dependence

(i) -------------- = x

(j) X : --------------

then i and j are anti – dependence

Hence I2 and I4 are anti-dependence

⇒ Anti-dependence create stall in pipeline

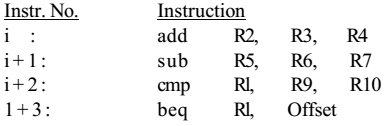

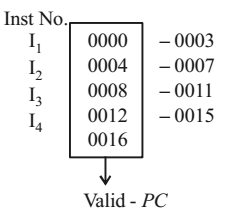

- Consider a RISC machine where each instruction is exactly 4 bytes long. Conditional and unconditional branch instructions use PC-relative addressing mode with Offset specified in bytes to the target location of the branch instruction. Further the Offset is always with respect to the address of the next instruction in the program sequence. Consider the following instruction sequence

If the target of the branch instruction is i, then the decimal value of the Offset is ______.

-

View Hint View Answer Discuss in Forum

In program storage,

Assuming the starting address (EA) is 0000, then

where, I4 is as branch instruction I1 as a target location.

So, PC-relative addressing mode is: (EA) = (PC) + relative value Relative value = (EA) – (PC) = 0000 – 0016 = –16.Correct Option: A

In program storage,

Assuming the starting address (EA) is 0000, then

where, I4 is as branch instruction I1 as a target location.

So, PC-relative addressing mode is: (EA) = (PC) + relative value Relative value = (EA) – (PC) = 0000 – 0016 = –16.

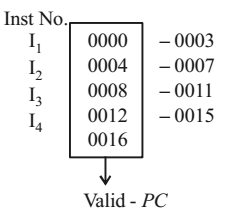

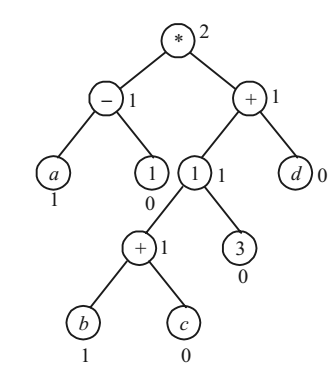

- Consider the expression (a – 1) * (((b + c)/ 3) + d)), Let X be the minimum number of registers required by an optimal code generation (without any register spill) algorithm tor a load/store architecture, in which

(i) only load and store instructions can have memory operands and

(ii) arithmetic instructions can have only register or immediate operands.

The value of X is______.

-

View Hint View Answer Discuss in Forum

The given expression is (1) *

b + c

+ d

3

Let R1 and R2 be two registers

Load R1 ← b

Load R2 ← c

Add R1 ← (R1 + R2)

Div. R1 ← R1 / 3

Load R2 ← d

Add R1 ← R1 + R2

Load R2 ← a

Sub. R2 ← R2 - 1

Mul. R1 ← R1 * R2

Hence, only two registers are required.Correct Option: C

The given expression is (1) *

b + c

+ d

3

Let R1 and R2 be two registers

Load R1 ← b

Load R2 ← c

Add R1 ← (R1 + R2)

Div. R1 ← R1 / 3

Load R2 ← d

Add R1 ← R1 + R2

Load R2 ← a

Sub. R2 ← R2 - 1

Mul. R1 ← R1 * R2

Hence, only two registers are required.

- A processor has 40 distinct instructions and 24 general purpose registers. A 32-bit instruction word has an opcode, two register operands and an immediate operand. The number of bits available for the immediate operand field is ________.

-

View Hint View Answer Discuss in Forum

6 bits are needed for 40 distinct instructions (because, 32 < 40 < 64) 5 bits are needed for 24 general purpose registers (because, 16 < 24 < 32) 32-bit instruction word has an opcode(6 bit), two register operands(total 10 bits) and an immediate operand (x bits). The number of bits available for the immediate operand field => x = 32 – (6 + 10) = 16 bits

Correct Option: B

6 bits are needed for 40 distinct instructions (because, 32 < 40 < 64) 5 bits are needed for 24 general purpose registers (because, 16 < 24 < 32) 32-bit instruction word has an opcode(6 bit), two register operands(total 10 bits) and an immediate operand (x bits). The number of bits available for the immediate operand field => x = 32 – (6 + 10) = 16 bits