Computer organization and architecture miscellaneous

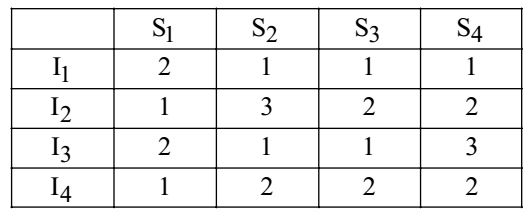

- Consider a 4 stage pipeline processor. The number of cycles needed by the four instructions I1, I2 , I3 , I4 in stages S1 , S2 , S3 , S4 is shown below.

What is the number of cycles needed to execute the following loop ?

For (i = 1 to 2) {I1; I2; I3; I4;}

-

View Hint View Answer Discuss in Forum

Here bound of the loop are constants, therefore compiler will do the loop un rolling (if compiler won't then prefetcher will do) to increase the instruction level parallelism. And after loop unrolling 23 cycles are required for execution. Therefore option (b) is the correct answer.

Correct Option: B

Here bound of the loop are constants, therefore compiler will do the loop un rolling (if compiler won't then prefetcher will do) to increase the instruction level parallelism. And after loop unrolling 23 cycles are required for execution. Therefore option (b) is the correct answer.

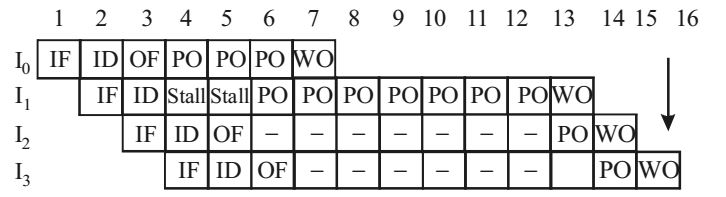

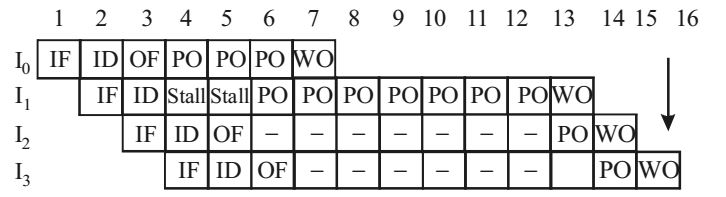

- A 5-stage pipelined processor has Instruction Fetch (IF), Instruction Decode (ID), Operand Fetch (OF), Perform Operation (PO) and Write Operand (WO) stages. The IF, ID, OF and WO stages take 1 clock cycle each for any instruction. The PO stage takes 1 clock cycle for ADD and SUB instructions, 3 clock cycles for MUL instruction, and 6 clock cycles for DIV instruction respectively. Operand forwarding is used in the pipeline. What is the number of clock cycles needed to execute the following sequence of the instructions ?

Instruction Meaning of instruction I0 : MUL R2, R0 , R1 R2 → R0 * R1 I1 : DIV R5, R3, R4 R5 → R3 / R4 I2 : ADD R2 , R5, R2 R2 → R5 + R2 I3 : SUB R5, R2, R6 R5 → R2 – R6

-

View Hint View Answer Discuss in Forum

As per the given, the instructions are arranged accordingly to their meanings. We get the following :

Here, we can see that the last operation (Write Operand) comes at the 15th clock cycle so it takes 15 clock cycles to execute given sequence of instructions.Correct Option: B

As per the given, the instructions are arranged accordingly to their meanings. We get the following :

Here, we can see that the last operation (Write Operand) comes at the 15th clock cycle so it takes 15 clock cycles to execute given sequence of instructions.

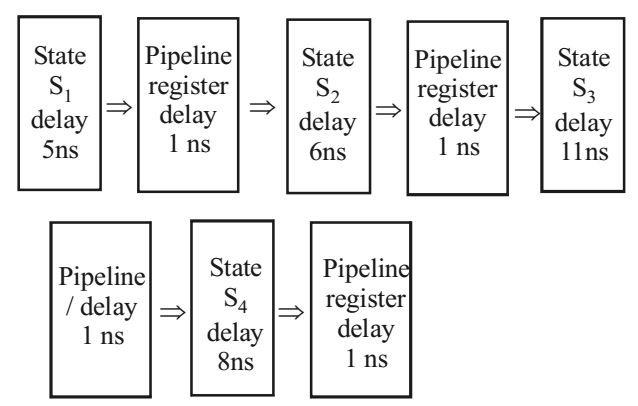

- Consider an instruction pipeline with four stages (S1 , S2 , S3 and S4) each with combinational circuit only. The pipeline registers are required between each stage and at the end of the last stage. Delays for the stages and for the pipeline registers are as given in the figure

What is the approximate speed up of the pipeline in steady state under ideal conditions when compared to the corresponding non-pipeline implementation?

-

View Hint View Answer Discuss in Forum

Speed up = (5 + 6 + 11 + 8) = 30 = 2.5 (11 + 1) 12 Correct Option: B

Speed up = (5 + 6 + 11 + 8) = 30 = 2.5 (11 + 1) 12

- Register renaming is done in pipelined processors

-

View Hint View Answer Discuss in Forum

Pipelining of the register renaming logic can help avoid restricting the processor clock frequency.

Correct Option: C

Pipelining of the register renaming logic can help avoid restricting the processor clock frequency.

- Consider the following sequence of micro-operations.

MBR ← PC

MAR ← X

PC ← Y

Memory ← MBR

Which one of the following is a possible operation performed by this sequence ?

-

View Hint View Answer Discuss in Forum

The following sequence of micro-operations

MBR ← PC

MAR ← X

PC ← Y

Memory ← MBR.

Analysis

1. First micro operation stores the value of PC into Memory Base Register (MBR).

2. Second micro operation stores the value of X into Memory Address Resister (MAR).

3. Third micro operation stores value of Y into PC.

4. Fourth micro operation stores value of MBR to memory.

So before execution of these instructions PC holds the value of next instruction to be executed. We first stores the value of PC to MBR and then through MBR to memory i.e., We are saving the value of PC in memory and then load PC with a new value. This can be done only in two types. Operations Conditional branch and interrupt service.

As we are not checking here for any conditions. So, it is an Initiation of interrupt service.Correct Option: D

The following sequence of micro-operations

MBR ← PC

MAR ← X

PC ← Y

Memory ← MBR.

Analysis

1. First micro operation stores the value of PC into Memory Base Register (MBR).

2. Second micro operation stores the value of X into Memory Address Resister (MAR).

3. Third micro operation stores value of Y into PC.

4. Fourth micro operation stores value of MBR to memory.

So before execution of these instructions PC holds the value of next instruction to be executed. We first stores the value of PC to MBR and then through MBR to memory i.e., We are saving the value of PC in memory and then load PC with a new value. This can be done only in two types. Operations Conditional branch and interrupt service.

As we are not checking here for any conditions. So, it is an Initiation of interrupt service.