Computer organization and architecture miscellaneous

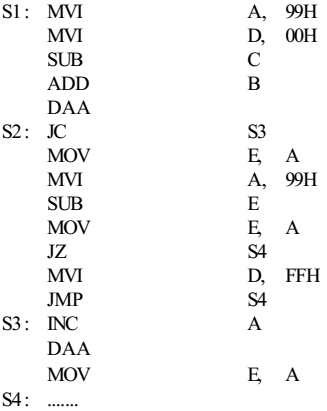

- Consider the following 8085 program segment, where registers B and C contain BCD values :

(a) For the two pairs (B = 44, C = 25) and (B = 33, C = 46) at S1,

(i) Find the values in register A when control reaches S2.

(ii) Find the values in registers D and E when control reaches S4.

(b) What, in general, is the value of D and E as a function of B and C when control reaches S4.

-

View Hint View Answer Discuss in Forum

(a) (i) 18 H 86H

(ii) D = 00H D = FFH

E = 19H E 13H

(b) E = | B – C |

D = 00H if B > C

and D = FFH if B < CCorrect Option: D

(a) (i) 18 H 86H

(ii) D = 00H D = FFH

E = 19H E 13H

(b) E = | B – C |

D = 00H if B > C

and D = FFH if B < C

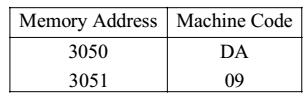

- Consider the 8085 instruction IN 09H stored as follows:

Add the following incomplete timing diagram for the instruction :

(a) Write the contents of the boxes, A, B, C and D in hexademcimal in your answer sheet do not draw any pictures.

(b) Write the state of both ALE and RD pins at times T1, T2, T3 and T4. (c) How do you generate the signal that tells the peripheral to put the data on the bus? Answer by completing the following statement in your answer book : By combining signals ..............

-

View Hint View Answer Discuss in Forum

(a) A : D A H B : 0 9 H

C : 0 9 H D : 5 1 H

(b) ALE : T1 = 1

T2 = T3 = T4 = 0

RD : T1 = 1

T2 = T3 = 0. T4 = 1

(c) The IO/ M signal and RD signalCorrect Option: D

(a) A : D A H B : 0 9 H

C : 0 9 H D : 5 1 H

(b) ALE : T1 = 1

T2 = T3 = T4 = 0

RD : T1 = 1

T2 = T3 = 0. T4 = 1

(c) The IO/ M signal and RD signal

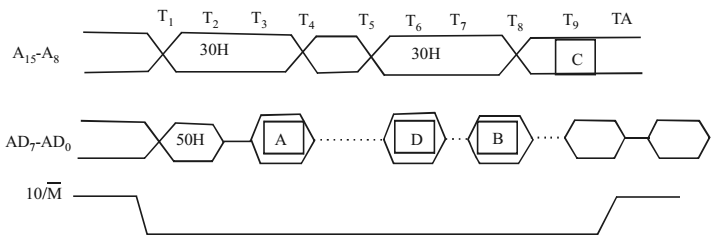

- Which is the most appropriate match for the items in the first column with the items in the second column?

-

View Hint View Answer Discuss in Forum

Indexed addressing is used for array implementation where each element has indexes. Base register is used to re-locatable code, where starts from base address & then all local addresses as added to base address.

Indirect addressing is done when array is passed as parameter only name is passed. Hence (a) is correct option.Correct Option: A

Indexed addressing is used for array implementation where each element has indexes. Base register is used to re-locatable code, where starts from base address & then all local addresses as added to base address.

Indirect addressing is done when array is passed as parameter only name is passed. Hence (a) is correct option.

- A machine has a 32-bit architecture, with 1-word long instructions. It has 64 registers, each of which is 32 bits long. It needs to support 45 instructions, which have an immediate operand in addition to two register operands. Assuming that the immediate operand is an unsigned integer, the maximum value of the immediate operand is ______ .

-

View Hint View Answer Discuss in Forum

(i) Given is 32-bit architecture machine with 1 word long instruction; so, the instruction size is 32 bit.

(ii) As the machine need to support 45 instructions, the number of bits required in the “opcode field” is 6 bits, because,

5-bits: 25 = 32 (Not sufficient)

6-bits: 26 = 64 (Sufficient)

(iii) As the machine has 64 registers, so to uniquely identify a register out of those 64 registers, we need 6-bits. (using the similar argument as above) As each instruction has 2 register operands, so 6 + 6 = 12 bits are needed for them. So, finally instruction will took like as follows:

(Total = 32 bits)

(iv) As 14-bits are available for immediate operand, the max value will be 214 = 16384. However one value will be used for “Zero” also as the operand is an “unsigned integer”. So, finally, the maximum value that the immediate operand can take = 214 – 1 = 16383.Correct Option: C

(i) Given is 32-bit architecture machine with 1 word long instruction; so, the instruction size is 32 bit.

(ii) As the machine need to support 45 instructions, the number of bits required in the “opcode field” is 6 bits, because,

5-bits: 25 = 32 (Not sufficient)

6-bits: 26 = 64 (Sufficient)

(iii) As the machine has 64 registers, so to uniquely identify a register out of those 64 registers, we need 6-bits. (using the similar argument as above) As each instruction has 2 register operands, so 6 + 6 = 12 bits are needed for them. So, finally instruction will took like as follows:

(Total = 32 bits)

(iv) As 14-bits are available for immediate operand, the max value will be 214 = 16384. However one value will be used for “Zero” also as the operand is an “unsigned integer”. So, finally, the maximum value that the immediate operand can take = 214 – 1 = 16383.

- Consider a hypothetical processor with an instruction of type LW (R1), 20 (R2). which during execution reads a 32- bit word from memory and stores it in a 32-bit register R1. The effective address of the memory location is obtained by the addition of constant 20 and the contents of register R2. Which of the following best reflects the addressing mode implemented by this instrument for the operand in memory?

-

View Hint View Answer Discuss in Forum

The addressing mode will be base index addressing. Here, 20 will work as base and content of R2 will be index. R2 is base regester here and indexing is done by adding 20 to the contents of R2.

Correct Option: D

The addressing mode will be base index addressing. Here, 20 will work as base and content of R2 will be index. R2 is base regester here and indexing is done by adding 20 to the contents of R2.