Computer organization and architecture miscellaneous

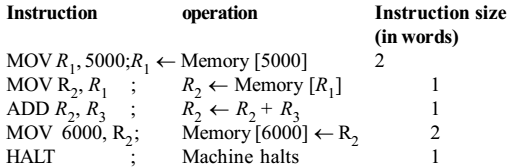

Direction: Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

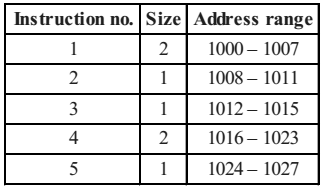

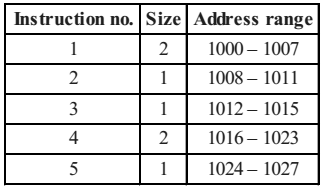

- Consider that the memory is byte addressable with size 32 bit, and the program has been loaded starting from memory location 1000 (decimal). If an Interrupt occurrs while the CPU has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

-

View Hint View Answer Discuss in Forum

Byte addressable so 1 word require 4 bytes.

Next location 1028. CPU has executed the HALT instruction so next time the CPU will resume at next location i.e. 1028 which would be at the top of stack. Hence (d) is correct option.Correct Option: D

Byte addressable so 1 word require 4 bytes.

Next location 1028. CPU has executed the HALT instruction so next time the CPU will resume at next location i.e. 1028 which would be at the top of stack. Hence (d) is correct option.

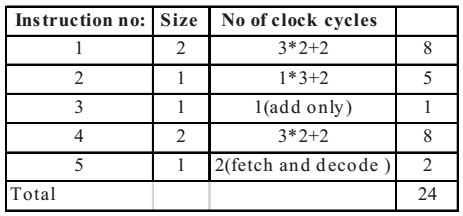

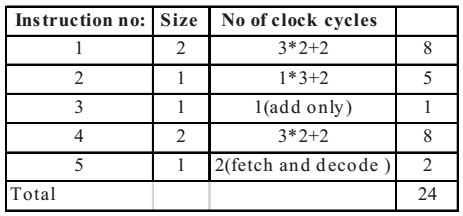

- Let the clock cycles required for vavious operations be as follows: Register to/from memory transfer: 3 clock cycles

Add with both operands in register: 1 clock cycle

Instruction fetch and decode: 2 clock cycles per word

The total number of clock cycles requires to execute the program is

-

View Hint View Answer Discuss in Forum

The clock cycles are per block so if an instruction size is 2 then it requires twice no. of clock cycles.

Correct Option: B

The clock cycles are per block so if an instruction size is 2 then it requires twice no. of clock cycles.

- Which of the following addressing modes are suitable for program relocation at run time?

1. Absolute addressing

2. Relative addressing

3. Based addressing

4. Indirect addressing

-

View Hint View Answer Discuss in Forum

Program relocation at run time transfers complete block to some memory locations. Relocation is the process of assigning load addresses to various parts of a program and adjusting the code and data in the program to reflect the assigned addresses This require base address and block should be relatively addressed through this base address. This require both based addressing and relative addressing mode. Hence (c) is correct option.

Correct Option: C

Program relocation at run time transfers complete block to some memory locations. Relocation is the process of assigning load addresses to various parts of a program and adjusting the code and data in the program to reflect the assigned addresses This require base address and block should be relatively addressed through this base address. This require both based addressing and relative addressing mode. Hence (c) is correct option.

- For a pipelined CPU with a single ALU, consider the following situations

1. The j + 1st instruction uses the result of the j th instruction as an operand.

2. The execution of a conditional jump instruction.

3. The j th and (j + 1) st instrution require the ALU at the same time. Which of the above can cause a hazard?

-

View Hint View Answer Discuss in Forum

Case 1 is here of data dependency, this can’t be safe with single ALU so read after write.

Case 2 Conditional jumps are always hazardous as they create conditional dependency in pipeline.

Case 3 This is write after read problem or concurrency dependency so hazardous. All the three are hazardous. Hence (d) is correct option.Correct Option: D

Case 1 is here of data dependency, this can’t be safe with single ALU so read after write.

Case 2 Conditional jumps are always hazardous as they create conditional dependency in pipeline.

Case 3 This is write after read problem or concurrency dependency so hazardous. All the three are hazardous. Hence (d) is correct option.

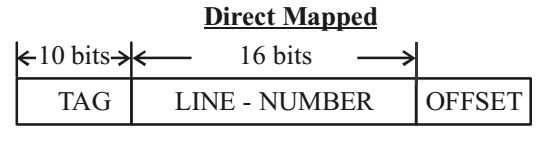

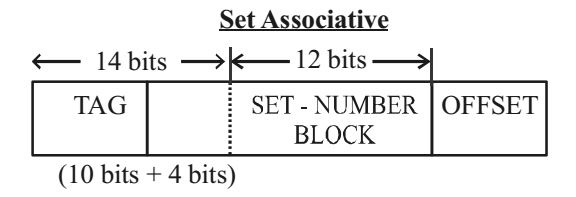

- A cache memory unit with capacity of N words and block size of B words is to be designed. If it is designed as a direct mapped cache, the length of the TAG field is 10 bits. If the cache unit is now designed as a 16-way set-associative cache, the length of the TAG field is______ bits.

-

View Hint View Answer Discuss in Forum

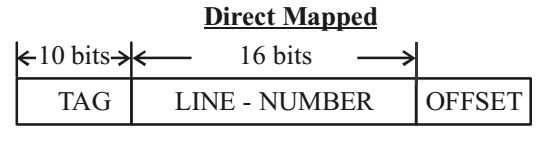

In Direct Mapped :

No. of line in direct mapped cache =

N

bits B For No. of line = log

N

B

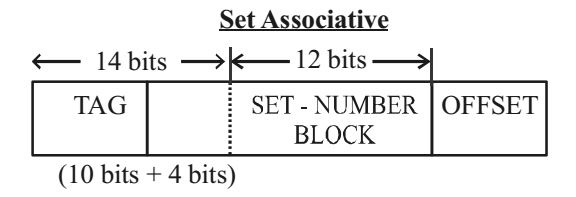

In Set Associative :

TAG1 + log

N

+ log(B) = TAG2 + log

N

+ log(B) B 16 B

By cancelling the same terms

As given that

TAG1 = 10 bits for Direct Mapping.

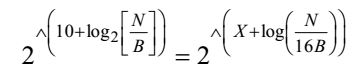

TAG2 let say X bits.Then , 10 + log

N

= X + log

N

B 16 B

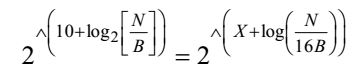

By taking exponentation both side w.r.t 2.

(2^10)*

N

= (2^X)*

N

B 16 B (2^10) = (2^X)

1

16 (2^10) = (2^X)

1

2^4

(2^14) = (2^X)X = 14

So, the required length of TAG field in Set Associative mapped is = 14.

Correct Option: C

In Direct Mapped :

No. of line in direct mapped cache =

N

bits B For No. of line = log

N

B

In Set Associative :

TAG1 + log

N

+ log(B) = TAG2 + log

N

+ log(B) B 16 B

By cancelling the same terms

As given that

TAG1 = 10 bits for Direct Mapping.

TAG2 let say X bits.Then , 10 + log

N

= X + log

N

B 16 B

By taking exponentation both side w.r.t 2.

(2^10)*

N

= (2^X)*

N

B 16 B (2^10) = (2^X)

1

16 (2^10) = (2^X)

1

2^4

(2^14) = (2^X)X = 14

So, the required length of TAG field in Set Associative mapped is = 14.