-

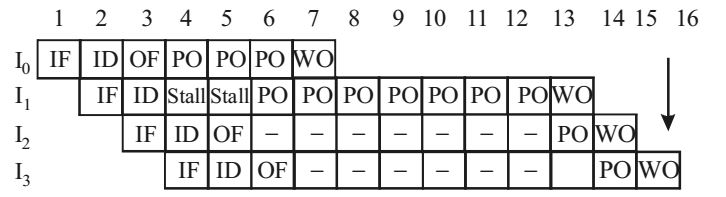

A 5-stage pipelined processor has Instruction Fetch (IF), Instruction Decode (ID), Operand Fetch (OF), Perform Operation (PO) and Write Operand (WO) stages. The IF, ID, OF and WO stages take 1 clock cycle each for any instruction. The PO stage takes 1 clock cycle for ADD and SUB instructions, 3 clock cycles for MUL instruction, and 6 clock cycles for DIV instruction respectively. Operand forwarding is used in the pipeline. What is the number of clock cycles needed to execute the following sequence of the instructions ?

Instruction Meaning of instruction I0 : MUL R2, R0 , R1 R2 → R0 * R1 I1 : DIV R5, R3, R4 R5 → R3 / R4 I2 : ADD R2 , R5, R2 R2 → R5 + R2 I3 : SUB R5, R2, R6 R5 → R2 – R6

-

- 13

- 15

- 17

- 19

- 13

Correct Option: B

As per the given, the instructions are arranged accordingly to their meanings. We get the following :

Here, we can see that the last operation (Write Operand) comes at the 15th clock cycle so it takes 15 clock cycles to execute given sequence of instructions.