Advanced Microprocessors

- The number of comparator carried out in a 4 bit flashtype A/D converter is—

-

View Hint View Answer Discuss in Forum

No. of comparator required = 2n – 1

(where, n = no. of bits)

= 24 – 1 = 15

Hence alternative (B) is the correct answer.Correct Option: B

No. of comparator required = 2n – 1

(where, n = no. of bits)

= 24 – 1 = 15

Hence alternative (B) is the correct answer.

- Among the following the slowest ADC is—

-

View Hint View Answer Discuss in Forum

Integrating type ADC are more accurate but slow.

Correct Option: C

Integrating type ADC are more accurate but slow.

- Which of the following is D to A conversion technique?

-

View Hint View Answer Discuss in Forum

Among the given, weighted resistor technique is only D to A conversion technique.

Correct Option: B

Among the given, weighted resistor technique is only D to A conversion technique.

- For an input pulse train of clock period T, the delay produced by an n stage shift register—

-

View Hint View Answer Discuss in Forum

nT, Because in the case of shift register all the flipflops are connected in cascaded fashion.

Correct Option: B

nT, Because in the case of shift register all the flipflops are connected in cascaded fashion.

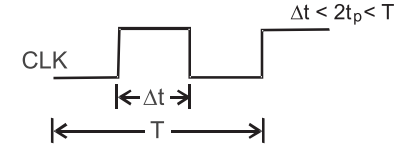

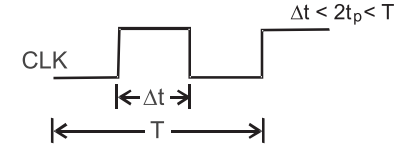

- Which of the following condition must be met to avoid race around problem where, tp is propagation delay of the NAND gate, Δt is pulse width and T is period of pulse train?

-

View Hint View Answer Discuss in Forum

Condition to avoid race around problem:

where, Δt = Pulse width

T = Period of pulse

2tp = Propagation delay of two NAND gates or flip-flop.

It may be noted that tp is the propagation delay of one gate. However any flip-flop made up of 4 NAND gates or NOR gates, and any input passes through 2 gates, that's why here we must take 2tp propagation delay.Correct Option: B

Condition to avoid race around problem:

where, Δt = Pulse width

T = Period of pulse

2tp = Propagation delay of two NAND gates or flip-flop.

It may be noted that tp is the propagation delay of one gate. However any flip-flop made up of 4 NAND gates or NOR gates, and any input passes through 2 gates, that's why here we must take 2tp propagation delay.