Advanced Microprocessors

- Implement Y = A + BC + AC requires minimum number of NAND gate are—

-

View Hint View Answer Discuss in Forum

Given,

or Y = A + AC + BC

or Y = A (1 + C) + BC

or Y = A + BC

So, the minimum number of NAND gates requirement is 4. Hence alternative (A) is correct choice.Correct Option: A

Given,

or Y = A + AC + BC

or Y = A (1 + C) + BC

or Y = A + BC

So, the minimum number of NAND gates requirement is 4. Hence alternative (A) is correct choice.

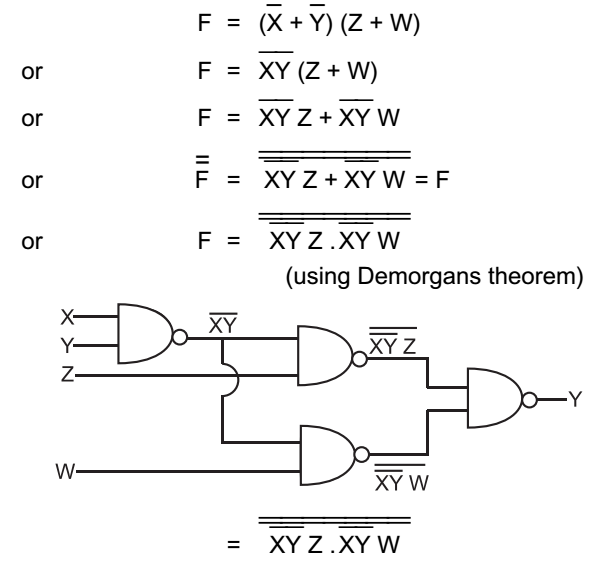

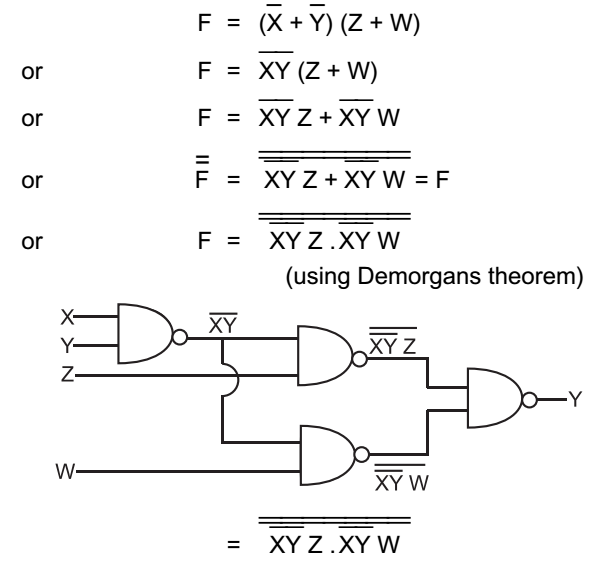

- Minimum number of 2-input NAND gates required to implement the function F = (X +Y) (Z + W)

-

View Hint View Answer Discuss in Forum

In order to solve such type of problem first reduce any from into SOP (sum of product form) and then take double complement on that reduced from.

NOTE: No. of complement means number of NAND gate through which it passes.

So, the number of NAND gate requirement is equal to 4.Correct Option: B

In order to solve such type of problem first reduce any from into SOP (sum of product form) and then take double complement on that reduced from.

NOTE: No. of complement means number of NAND gate through which it passes.

So, the number of NAND gate requirement is equal to 4.

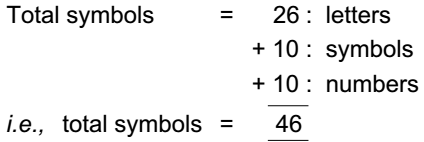

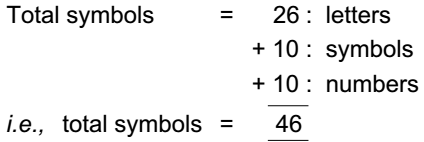

- The number of bits needed to encode all letters (i.e., 26), 10 symbols and all number (i.e.,10) is—

-

View Hint View Answer Discuss in Forum

⇒ n = 6, as 26 = 64

if we take n = 5, then 25 = 32 which will not encode 46 number, hence n = 6 taken.Correct Option: C

⇒ n = 6, as 26 = 64

if we take n = 5, then 25 = 32 which will not encode 46 number, hence n = 6 taken.

- The switching speed of ECL is very high, because—

-

View Hint View Answer Discuss in Forum

Refer synopsis

Correct Option: C

Refer synopsis

- A 4 bit synchronous counter uses flip-flop with propagation delay time of 25 ns each. The maximum possible time required for change of state will be—

-

View Hint View Answer Discuss in Forum

Total propagation delay = 25 × 4 ns = 100 ns

Correct Option: D

Total propagation delay = 25 × 4 ns = 100 ns