Digital circuits miscellaneous

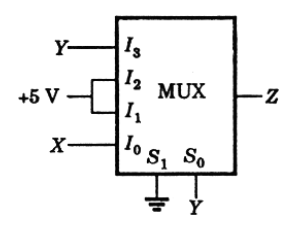

- The output of the 4 × 1 multiplexer shown in the figure, is

-

View Hint View Answer Discuss in Forum

Z = XY + XY + XY,

Z = X + YCorrect Option: A

Z = XY + XY + XY,

Z = X + Y

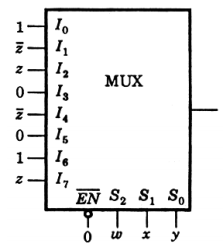

- The 8-to-1 multiplexer shown in the figure, realize which of the following Boolean expression?

-

View Hint View Answer Discuss in Forum

Let z = 0

Then ƒ = wxy + wxy + wxy + wxy = wx + wy

If we put z = 0 in given option, then

(a) = wx + xy (b) = wy + wxy (c) = wx + wy

Since MUX is enable.Correct Option: C

Let z = 0

Then ƒ = wxy + wxy + wxy + wxy = wx + wy

If we put z = 0 in given option, then

(a) = wx + xy (b) = wy + wxy (c) = wx + wy

Since MUX is enable.

- A retriggerable monoshot is one which

-

View Hint View Answer Discuss in Forum

NA

Correct Option: D

NA

- A 4-bit-synchronous counter uses flip-flops with pr opagation delay time of 25 ns each. The maximum possible time required for change of state will be

-

View Hint View Answer Discuss in Forum

NA

Correct Option: A

NA

- A full-adder can be implemented with half-adders and OR gates. A 4-bit parallel full adder without any initial carry requires

-

View Hint View Answer Discuss in Forum

The circuit of a 4-bit full adder using half adders and OR gates is shown in the figure

From the figure, it is apparent that 4-bit full adder required seven half adders and 3-OR gates.

Correct Option: D

The circuit of a 4-bit full adder using half adders and OR gates is shown in the figure

From the figure, it is apparent that 4-bit full adder required seven half adders and 3-OR gates.