Digital electronics miscellaneous

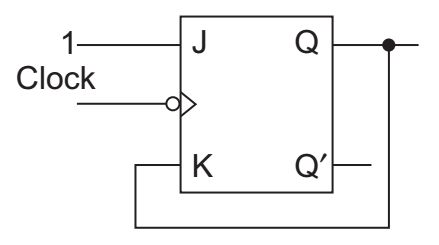

- For one of the following conditions, clocked J-K flip-flop can be used as a divide-by-2 circuit when the input signal is applied at clock-input—

-

View Hint View Answer Discuss in Forum

The clocked J-K flip-flop can be used as a divide-by- 2 circuit when input J = K = 1 is applied at clock input and flip-flop has active HIGH inputs.

Correct Option: A

The clocked J-K flip-flop can be used as a divide-by- 2 circuit when input J = K = 1 is applied at clock input and flip-flop has active HIGH inputs.

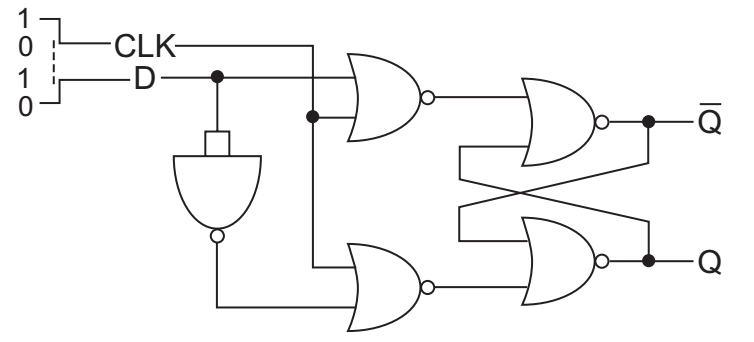

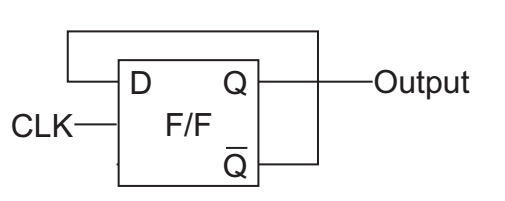

- For the circuit shown below, D has a transition from 0 to 1 after CLK changes from 1 to 0. Assume gate delays to be negligible Which of the following statements in true?

-

View Hint View Answer Discuss in Forum

The given circuit

From the given circuit we conclude that Q goes to 1 at the CLK transition and goes to 0 when D goes to 1.

Correct Option: C

The given circuit

From the given circuit we conclude that Q goes to 1 at the CLK transition and goes to 0 when D goes to 1.

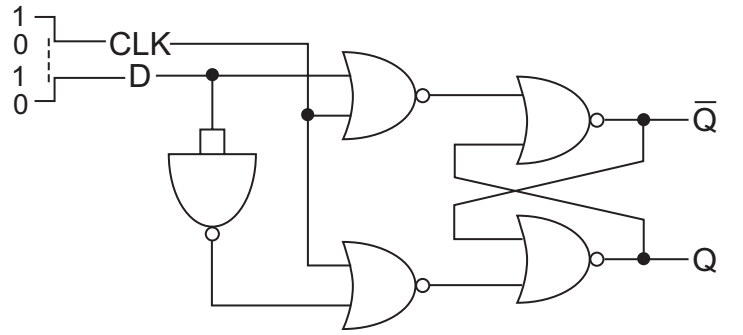

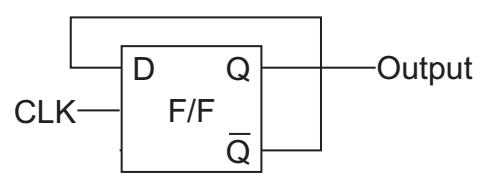

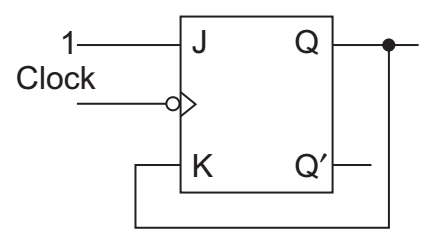

- For the circuit shown below what is the frequency of the output Q?

-

View Hint View Answer Discuss in Forum

The given circuit

The frequency of the output is half the input clock frequency.

Correct Option: B

The given circuit

The frequency of the output is half the input clock frequency.

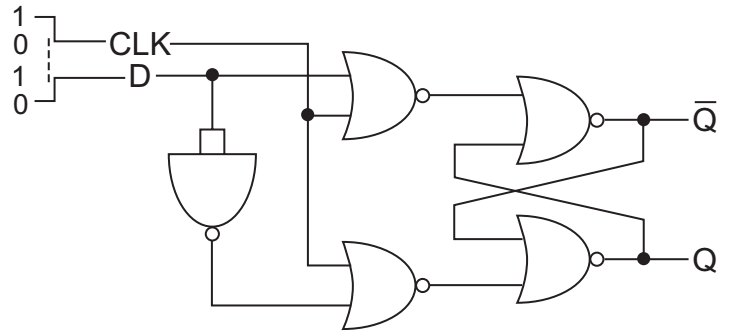

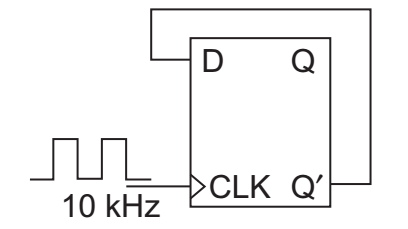

- The frequency of the clock signal applied to the rising edge triggered D flip-flop shown below is 10 kHz. What is the frequency of the signal available at Q?

-

View Hint View Answer Discuss in Forum

Output frequency = Fs 2 = 10 kHz 2 = 5 kHz

Output frequency = Fs = 10 kHz = 5 kHz 2 2 Correct Option: B

Output frequency = Fs 2 = 10 kHz 2 = 5 kHz

Output frequency = Fs = 10 kHz = 5 kHz 2 2

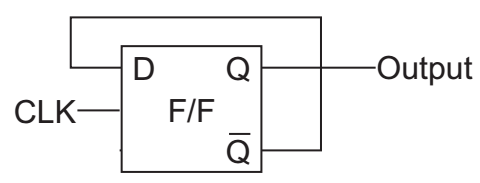

- For the circuit shown below, Q = 0 initially. What shall be the subsequent states of Q when clock pulses are given?

-

View Hint View Answer Discuss in Forum

The given circuit

Given that initially flip-flop is cleared i.e., Q = 0. After applying the CLK pulses, we get 1, 0, 1, 0......

Correct Option: A

The given circuit

Given that initially flip-flop is cleared i.e., Q = 0. After applying the CLK pulses, we get 1, 0, 1, 0......