8085 microprocessor miscellaneous

- The ____ number of address lines are needed to address each memory location in a 2048 × 4 memory chip

-

View Hint View Answer Discuss in Forum

NA

Correct Option: D

NA

- An output device is interfaced with 8-bit microprocessor 8085A. The interfacing circuit is shown in figure

The interfacing circuit makes use of 3 Line to 8 Line decoder having 3 enable lines E1 ,E2 ,E3. The address of the device is

-

View Hint View Answer Discuss in Forum

To enable 3L × 8L decoder, three enable lines E1 (which is connected as an output of AND-gate)

should be HIGH and E2 and E3 should be active low, it means I0/m should be active low which is indicating that it is memory mapped I/O interfacing. So address of the device will be in 16-bits. To select output port through decoder 2nd line the status of A15 (I2) A14(I1) A13(I0) = 010 and to enable decoder through E1 enable line A12 = 1 and A11 = 0 and by default as a starting address other address lines (A10......A0) shold be zero. So, overall port address is

Correct Option: B

To enable 3L × 8L decoder, three enable lines E1 (which is connected as an output of AND-gate)

should be HIGH and E2 and E3 should be active low, it means I0/m should be active low which is indicating that it is memory mapped I/O interfacing. So address of the device will be in 16-bits. To select output port through decoder 2nd line the status of A15 (I2) A14(I1) A13(I0) = 010 and to enable decoder through E1 enable line A12 = 1 and A11 = 0 and by default as a starting address other address lines (A10......A0) shold be zero. So, overall port address is

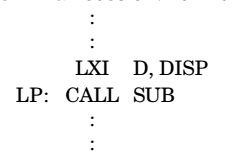

- A portion of the main program to call a subroutine SUB in an 8085 environment is given below. :

It is desired that control be returned to LP + DISP + 3 when the RET instruction is executed in the subroutine. The set of instructions that precede the RET instruction in the subroutine are

-

View Hint View Answer Discuss in Forum

NA

Correct Option: C

NA

- In an 8085 microprocessor, the contents of the Accumulator, after the following instructions are executed will become

XRA A

MVIB F0H

SUB B

-

View Hint View Answer Discuss in Forum

XRA A

A ← 00

MVIBF0

B ← F0

SUB B

A ← A – B

A ← A + (2’s complement to B)

A = 00000000

B = 11110000

2’s complement of B = 00010000

∴ A + B = (10)HCorrect Option: D

XRA A

A ← 00

MVIBF0

B ← F0

SUB B

A ← A – B

A ← A + (2’s complement to B)

A = 00000000

B = 11110000

2’s complement of B = 00010000

∴ A + B = (10)H

- An input device is interfaced with Intel 8085A microprocessor as memory mapped I /O. The address of the device is 2500H. In order to input data from the device to accumul at or, the sequence of instructions will be

-

View Hint View Answer Discuss in Forum

L × 1 H, 2500H: the data 2500H is loaded into HL pair

MOV A,M: the content of memory location whose address is in HL pair, is moved to accumulator. So finally input data from device is moved to accumulator.Correct Option: A

L × 1 H, 2500H: the data 2500H is loaded into HL pair

MOV A,M: the content of memory location whose address is in HL pair, is moved to accumulator. So finally input data from device is moved to accumulator.