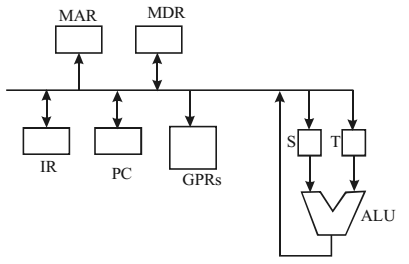

Direction: Consider the following data path of a CPU :

The ALU, the bus and all the registers in the data path are of identical size. All operations including incrementation of the PC and the GPRs are to be carried out in the ALU. Two clock cycles are needed for memory bus into the MDR.

-

The instruction “ADD R0, R1 ” has the register transfer interpretation R0 < = R0 + R1. The minimum number of clock cycles needed for execution cycle of this instruction is

-

- 2

- 3

- 4

- 5

- 2

Correct Option: B

Given that R0 ← R0 + R1 The clock cycles operate as follows :

| Cycle 1 | Out : R1 |

| In : S | |

| Cycle 2 | Out : R2 |

| In : T | |

| Cycle 3 | Out : S, T |

| Add : ALU | |

| In : R |

Therefore, execution cycle is completed in 3 clock cycles.