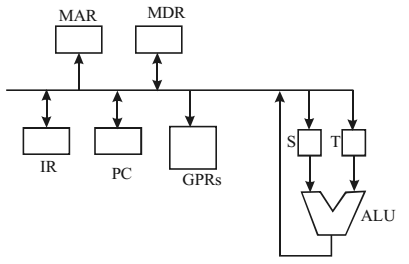

Direction: Consider the following data path of a CPU :

The ALU, the bus and all the registers in the data path are of identical size. All operations including incrementation of the PC and the GPRs are to be carried out in the ALU. Two clock cycles are needed for memory bus into the MDR.

-

The instruction “CALL Rn, sub” is a two word instruction. Assuming that PC is incremented during the fetch cycle of the first word of the instruction, its register transfer interpretation is Rn < = PC + 1 PC < = M [PC]

The minimum number of CPU clock cycles needed during the execution cycle of this instruction is

-

- 2

- 3

- 4

- 5

- 2

Correct Option: B

The minimum number of CPU clock cycles needed during the execution cycle = 4 As 1 cycle required to transfer already incremented value of PC and 2 cycle for getting data in MDR1 to load value of MDR in PC.