-

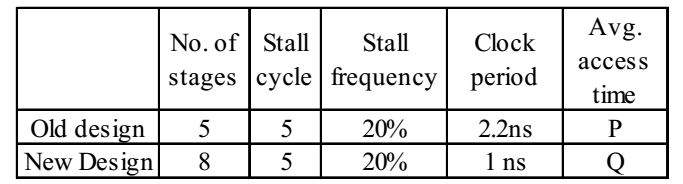

An instruction pipeline has five stages, namely, instruction fetch (IF), instruction decode and register fetch (ID/RF), instruction execution (EX), memory access (MEM), and register writeback (WB) with stage latencies 1 ns, 2.2 ns, 2 ns, 1 ns, and 0.75 ns, respectively (ns stands for nanoseconds). To gain in terms of frequency, the designers have decided to split the ID/RF stage into three stages (ID, RF1, RF2) each of latency 2.2/3 ns. Also, the EX stage is split into two stages (EX1, EX2) each of latency 1 ns. The new design has a total of eight pipeline stages. A program has 20% branch instructions which execute in the EX stage and produce the next instruction pointer at the end of the EX stage in the old design and at the end of the EX2 stage in the new design. The IF stage stalls after fetching a branch instruction until the next instruction pointer is computed. All instructions other than the branch instruction have an average CPI of one in both the designs. The execution times of this program on the old and the new design are P and Q nanoseconds, respectively. The value of P/Q is __________.

-

- 1.54

- 9.14

- 1.2

- 4.34

Correct Option: A

| P = |  | 80% (1 clock) + 20% |  | 1 completion | + | 2 stack clock |  |  | × Tc -p |

P = (0.8 + 0.6) × 2.2 ns = 3.08 ns

| Q = |  | 80% (1 clock) + 20% |  | 1 completion | + | 5 stack clock |  |  | × Tc -p |

P = (0.8 + 0.12) × 1 ns = 2 ns

| So the value of | = | = 1.54 | ||

| Q | 2 ns |