-

Consider a pipelined processor with the following four stages

IF : Instruction Fetch

ID : Instruction Decode and Operand Fetch

EX : Execute

WB : Write Black

The IF, ID and WB stages take 1 clock cycle each to complete the operation.

⚈ The number of clock cycle for the EX stage depends on the instruction. the ADD and SUB instructions need 1 clock cycle and the MUL instruction needs 3 clock cycles in the EX stage. Operand forwarding is used in the pipelined processor. What is the number of clock cycles taken to complete the following sequence of instructions:

-

- 7

- 8

- 10

- 14

- 7

Correct Option: B

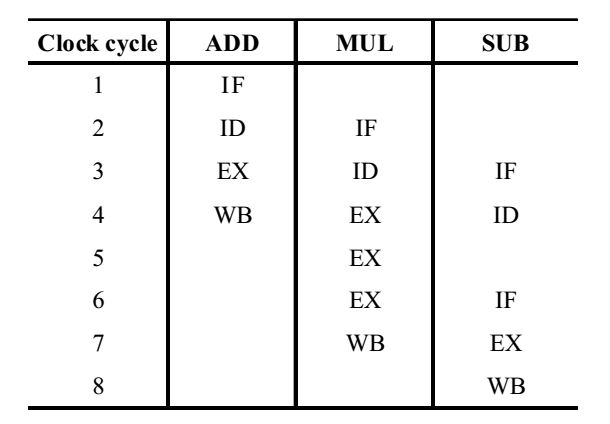

As given the pipelined processor has four stages i.e., IF, ID, EX, WB, And we know that number of clock cycles required to ADD and SUB instructions is 1 and by MUL instructions are 3.

In the pipelined processor while one instruction is fetched, the other is either being decoded or executed or some action is being performed. Thus, the number of cycles required by the given set of instructions can be obtained from the following diagram.

Thus, total number of clock cycles required are 8.