-

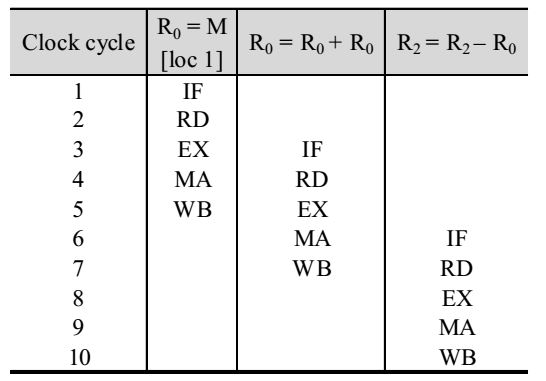

A 5 stage pipelined CPU has the following sequence of stages

IF : Instruction fetch from instruction memory

RD : Instruction decode and register read

EX: Execute: ALU operations for data and address computation

MA : Data memory access : for write access, the register read at RD stage is used

WB : Register write back

Consider the following sequence of instructions :

I1 : L R0 loc 1; R0 < = M [loc1]

I2 : A R0 ; R0 ; R0 < = R0 + R0

I3 : S R2; R0 ; R2 < = R2 – R0

Let each state takes on clock cycle.

What is the number of clock cycles taken to complete the above sequence of instructions starting from the fetch of I1 ?

-

- 8

- 10

- 12

- 15

- 8

Correct Option: A

Thus, total number of clock cycles required = 10